現(xiàn)貨庫存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

在CMOS集成電路應(yīng)用中,**Latch Up(閂鎖效應(yīng))**是一個(gè)極易被忽視但可能造成嚴(yán)重后果的寄生效應(yīng)。尤其在汽車電子等高可靠性要求場景中,這一問題尤為關(guān)鍵。與普通消費(fèi)類芯片不同,車規(guī)級芯片的規(guī)格書中通常會明確標(biāo)注其Latch Up承受能力,這也是評估其可靠性和抗干擾性能的重要指標(biāo)之一。

Latch Up是指CMOS結(jié)構(gòu)中存在的寄生雙極型晶體管(NPN和PNP)因異常偏置而觸發(fā)導(dǎo)通,形成從電源VDD到地GND之間的低阻通路。一旦觸發(fā),該通路將維持大電流流動,可能導(dǎo)致芯片永久損壞。

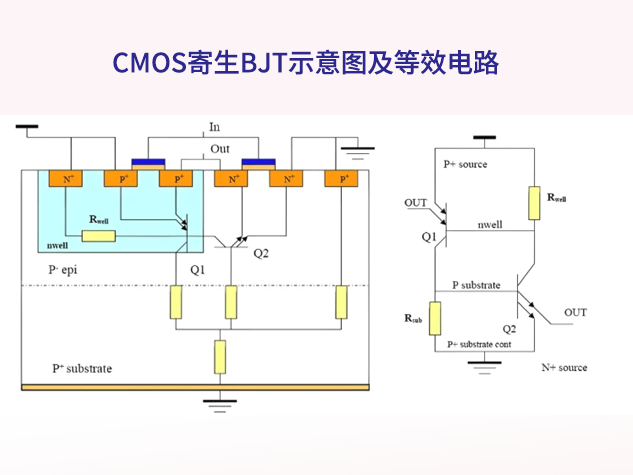

該效應(yīng)源于CMOS工藝本身結(jié)構(gòu)中的N-P-N-P可控硅結(jié)構(gòu)(如圖1所示),當(dāng)其中一個(gè)寄生BJT進(jìn)入正向?qū)顟B(tài)時(shí),可能引發(fā)正反饋,導(dǎo)致整個(gè)結(jié)構(gòu)進(jìn)入閂鎖狀態(tài)。

圖1 CMOS寄生BJT結(jié)構(gòu)及等效電路示意圖(注:圖片來源于網(wǎng)絡(luò))

靜電放電(ESD事件)

電源電壓瞬變

輸入/輸出信號超過供電電壓范圍

多電源系統(tǒng)上電順序不當(dāng)

一旦觸發(fā)Latch Up,唯一恢復(fù)方式是斷電重啟。若此時(shí)流經(jīng)閂鎖路徑的電流超過芯片設(shè)計(jì)所能承受的最大值,則可能造成永久性損壞。

雖然芯片設(shè)計(jì)階段已通過多種手段(如增加襯底接觸、隔離環(huán)、阱電阻優(yōu)化等)降低閂鎖風(fēng)險(xiǎn),但在實(shí)際應(yīng)用中仍需采取以下措施進(jìn)行有效防護(hù):

1. 輸入/輸出端加鉗位保護(hù)電路

為防止信號超出器件工作電壓范圍,建議在I/O口加入TVS管或鉗位二極管,限制輸入電壓不超過VDD+0.3V或低于GND-0.3V,從而避免觸發(fā)寄生結(jié)構(gòu)導(dǎo)通。

2. VDD電源去耦與濾波

電源噪聲、尖峰電壓是誘發(fā)Latch Up的重要誘因。因此,在芯片電源引腳附近應(yīng)布置高頻陶瓷電容(如100nF)進(jìn)行去耦,并結(jié)合磁珠或小電感構(gòu)成π型濾波,抑制高頻干擾。

3. 增設(shè)限流電阻

在VDD供電路徑中串聯(lián)一個(gè)限流電阻Rlimit,確保即使發(fā)生Latch Up,流經(jīng)芯片內(nèi)部寄生結(jié)構(gòu)的電流也不會超過其Latch Up耐受極限。此方法雖會略微影響壓降,但可顯著提升系統(tǒng)魯棒性。

4. 多電源系統(tǒng)的上電時(shí)序控制

對于采用多個(gè)電源域的系統(tǒng)(如IO電源、Core電源、模擬電源等),必須嚴(yán)格遵循**“先主電源后外圍”、“先芯片后外設(shè)”**的上電順序。關(guān)閉時(shí)則反之,以避免因信號驅(qū)動先于電源建立而導(dǎo)致寄生結(jié)構(gòu)異常導(dǎo)通。

Latch Up是CMOS器件固有的潛在失效機(jī)制,尤其在汽車電子等對功能安全要求嚴(yán)苛的應(yīng)用場景中更需引起重視。盡管芯片廠商在設(shè)計(jì)層面不斷優(yōu)化結(jié)構(gòu)以降低閂鎖風(fēng)險(xiǎn),但作為系統(tǒng)工程師,仍需在硬件設(shè)計(jì)中綜合考慮電壓鉗位、電源濾波、限流保護(hù)以及上電時(shí)序控制等多重防護(hù)措施,才能有效規(guī)避這一隱患。

在選擇車規(guī)級芯片時(shí),也應(yīng)特別關(guān)注其規(guī)格書中是否明確給出Latch Up測試等級(如JEDEC JESD78標(biāo)準(zhǔn)),以便更準(zhǔn)確地評估其在復(fù)雜電磁環(huán)境下的穩(wěn)定性與可靠性。