15年IC行業(yè)代理分銷(xiāo) 覆蓋全球300+品牌

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

24小時(shí)服務(wù)熱線(xiàn): 0755-82539998

現(xiàn)貨庫(kù)存,2小時(shí)發(fā)貨,提供寄樣和解決方案

熱搜關(guān)鍵詞:

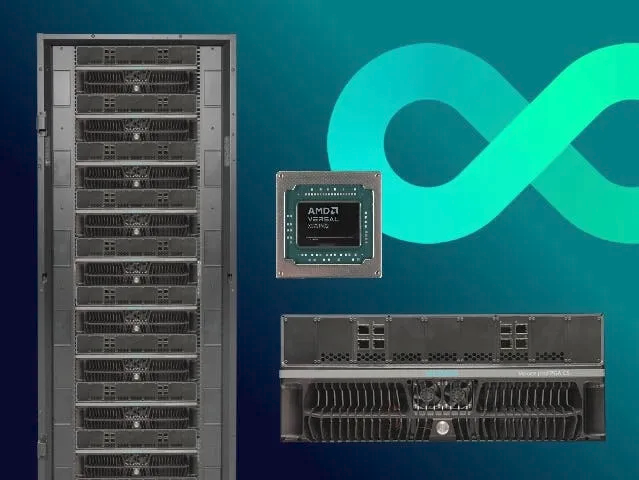

西門(mén)子的Veloce? proFPGA CS是一款專(zhuān)為軟件驗(yàn)證和軟硬件系統(tǒng)集成優(yōu)化的原型設(shè)計(jì)平臺(tái),基于AMD/XILINX的FPGA技術(shù),支持從單個(gè)FPGA到多刀片配置的各種設(shè)計(jì)規(guī)模。它通過(guò)模擬集成電路(IC)在不同輸入條件下的行為來(lái)測(cè)試和驗(yàn)證其設(shè)計(jì)功能,確保其按預(yù)期執(zhí)行,適用于各種復(fù)雜度的設(shè)計(jì)項(xiàng)目。

軟件驗(yàn)證過(guò)程通常涉及運(yùn)行周期準(zhǔn)確環(huán)境下的軟件工作負(fù)載來(lái)測(cè)試和驗(yàn)證SoC邏輯功能。仿真和基于FPGA的大規(guī)模原型設(shè)計(jì)是兩種主要的驗(yàn)證方法。仿真可以輕松將RTL編譯為可執(zhí)行模型,并具有全信號(hào)可觀測(cè)性,但執(zhí)行速度相對(duì)較慢。相比之下,基于FPGA的原型設(shè)計(jì)雖然靈活性較低,但能實(shí)現(xiàn)更高的執(zhí)行速度,這對(duì)于需要根據(jù)RTL設(shè)計(jì)驗(yàn)證代碼的軟件團(tuán)隊(duì)至關(guān)重要。

隨著AI、智能車(chē)輛和通用智能研究的發(fā)展,芯片設(shè)計(jì)的尺寸和復(fù)雜性顯著增加。對(duì)于系統(tǒng)廠商而言,不僅要驗(yàn)證RTL模塊,還需測(cè)試整個(gè)集成系統(tǒng),包括驅(qū)動(dòng)程序、操作系統(tǒng)及應(yīng)用軟件。這種需求的增長(zhǎng)促使了對(duì)更高效驗(yàn)證工具的需求。

1. 硬件與軟件協(xié)同開(kāi)發(fā)

西門(mén)子與AMD/XILINX合作開(kāi)發(fā)了Veloce proFPGA CS平臺(tái),該平臺(tái)采用了AMD Versal Premium VP1902自適應(yīng)SoC,具備高達(dá)前代器件兩倍的邏輯單元數(shù)量和I/O帶寬。這款高性能且完全可配置的系統(tǒng)允許設(shè)計(jì)人員在芯片可用之前通過(guò)大量軟件工作負(fù)載驗(yàn)證軟硬件集成。它提供了先進(jìn)的模塊化、可擴(kuò)展性和靈活性,滿(mǎn)足現(xiàn)代硬件和軟件工程師的驗(yàn)證需求。

首先,西門(mén)子獲得了AMD/XILINX Versal Premium VP1902器件的規(guī)格,隨后開(kāi)始開(kāi)發(fā)新款proFPGA CS平臺(tái)的硬件和軟件。獲取機(jī)械樣品后,西門(mén)子團(tuán)隊(duì)對(duì)其制造流程進(jìn)行了微調(diào)。接下來(lái),雙方團(tuán)隊(duì)在軟件方面進(jìn)行合作,具體而言是西門(mén)子編譯和綜合工具與用于布局布線(xiàn)的AMD/XILINX Vivado堆棧之間的接口。第三個(gè)合作領(lǐng)域是在調(diào)試方面,VP1902自適應(yīng)SoC提供了更高的邏輯單元數(shù)量和I/O帶寬。

2. 高性能與可擴(kuò)展性

Veloce proFPGA CS系統(tǒng)不僅易于部署,還能快速進(jìn)行IC和軟件的硅前驗(yàn)證。其超過(guò)1850萬(wàn)個(gè)邏輯單元、2000多個(gè)I/O以及最高可達(dá)112 Gbps速率的高速收發(fā)器,使其特別適合挑戰(zhàn)工程極限的應(yīng)用。此外,該系統(tǒng)還集成了Arm標(biāo)量處理器、PCIe Gen5、以太網(wǎng)和內(nèi)存接口的硬化IP,通過(guò)Versal可編程片上網(wǎng)絡(luò)簡(jiǎn)化大型設(shè)備中的數(shù)據(jù)移動(dòng)。

1. 提升驗(yàn)證效率

得益于Veloce proFPGA CS的高性能、高速接口和可擴(kuò)展性,軟件團(tuán)隊(duì)能夠在芯片可用之前對(duì)軟件進(jìn)行驗(yàn)證和調(diào)試。該系統(tǒng)可從單個(gè)FPGA或桌面上的單刀片擴(kuò)展到適用于多用戶(hù)環(huán)境的多刀片機(jī)架安裝配置。用戶(hù)可以根據(jù)項(xiàng)目的具體需求靈活定義FPGA數(shù)量、互連和高速協(xié)議接口,極大地提升了驗(yàn)證效率。

2. 促進(jìn)產(chǎn)品成功

西門(mén)子proFPGA CS產(chǎn)品經(jīng)理Romain Petit指出,AI在軟件流程中扮演重要角色,能夠?qū)㈦S機(jī)RTL設(shè)計(jì)映射到大型FPGA中,并利用AI提高結(jié)果質(zhì)量和編譯的可靠性和穩(wěn)定性。通過(guò)這種方式,Veloce proFPGA CS系統(tǒng)不僅加速了設(shè)計(jì)驗(yàn)證過(guò)程,還提高了最終產(chǎn)品的質(zhì)量。

3. 加速上市進(jìn)程

西門(mén)子原型設(shè)計(jì)產(chǎn)品戰(zhàn)略總監(jiān)Juergen Jaeger解釋道:“Veloce proFPGA CS系統(tǒng)可用于數(shù)據(jù)中心、實(shí)驗(yàn)室或臺(tái)式環(huán)境,能夠連接到PCIe等外部接口以及各類(lèi)外圍設(shè)備。當(dāng)今產(chǎn)品中的軟件內(nèi)容呈指數(shù)級(jí)增長(zhǎng),盡早驗(yàn)證軟件(又稱(chēng)‘左移’)是產(chǎn)品成功和加速上市進(jìn)程的關(guān)鍵。”

隨著AI和其他先進(jìn)技術(shù)的發(fā)展,芯片設(shè)計(jì)變得越來(lái)越復(fù)雜,傳統(tǒng)的驗(yàn)證方法已難以滿(mǎn)足需求。Veloce proFPGA CS作為一款高性能的原型設(shè)計(jì)平臺(tái),憑借其先進(jìn)的技術(shù)和高度的靈活性,為設(shè)計(jì)師提供了一個(gè)強(qiáng)大的工具,幫助他們應(yīng)對(duì)日益復(fù)雜的驗(yàn)證挑戰(zhàn)。無(wú)論是數(shù)據(jù)中心、實(shí)驗(yàn)室還是臺(tái)式環(huán)境,該系統(tǒng)都能有效提升驗(yàn)證效率,確保產(chǎn)品的成功和市場(chǎng)競(jìng)爭(zhēng)力。通過(guò)與AMD/XILINX的合作,西門(mén)子進(jìn)一步鞏固了其在電子設(shè)計(jì)自動(dòng)化領(lǐng)域的領(lǐng)先地位,推動(dòng)了下一代智能設(shè)備的發(fā)展。Veloce proFPGA CS系統(tǒng)的出現(xiàn),標(biāo)志著基于AMD/XILINX FPGA技術(shù)的芯片驗(yàn)證進(jìn)入了一個(gè)新的時(shí)代,為未來(lái)的技術(shù)創(chuàng)新奠定了堅(jiān)實(shí)的基礎(chǔ)。